# Modeling and SW Synthesis for Heterogeneous Embedded Systems in UML/MARTE

Tutorial SD1: High-Level Specifications to Cope With Design Complexity

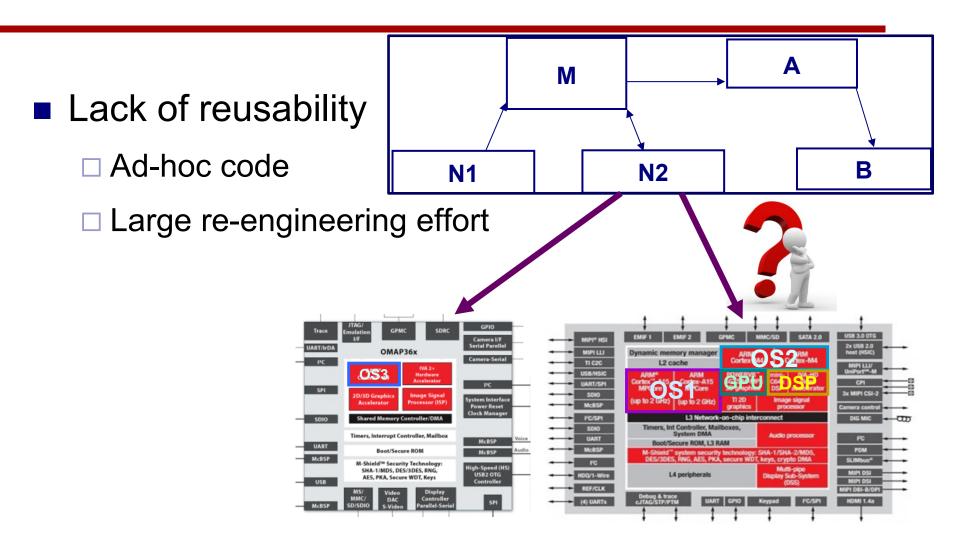

## **Motivation**

- Design productivity gap

Raising the abstraction level

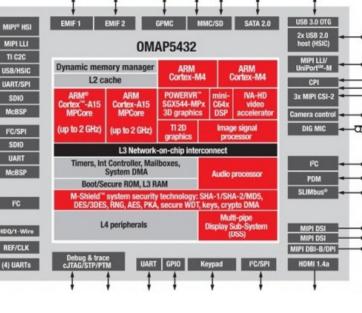

- Multi-Processing & Heterogeneous platforms

Increasing SW content

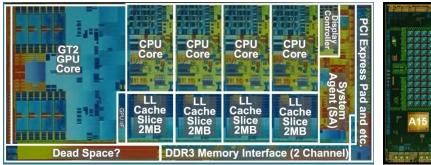

TI OMAP5432 SoC

□ SW-centric design methodologies

GPU

# **Usual SW development flow**

Costly fixing of wrong design decisions

# **Usual SW development flow**

### Outline

- Introduction

- State of the Art

- The PHARAON approach

- □ Design Flow

- Modeling Methodology

- □ SW Synthesis

- Conclusions

### Introduction

### Model-Driven Architecture (MDA)

□ High-abstraction level

□ Mature SW engineering methodology

### UML language

Application to embedded systems design

## Introduction

### • Why UML?

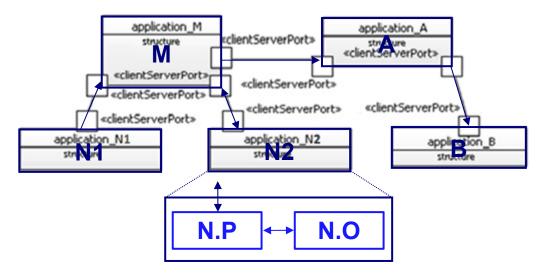

Natural way to capture system architecture

□ Standard way

application\_A

application\_B

structure

structure «clientServerPort»

## Introduction

### Why UML?

Natural way to capture system architecture

Standard way

UML language

application M

structure

clientServerPort>

- Semantics lacks

- What is each component?

- What kind or interaction each link actually means?

- Domain-specific profiles

- UML/MARTE

## Introduction

### MARTE MARTE

□ Standard UML profile for real-time embedded systems

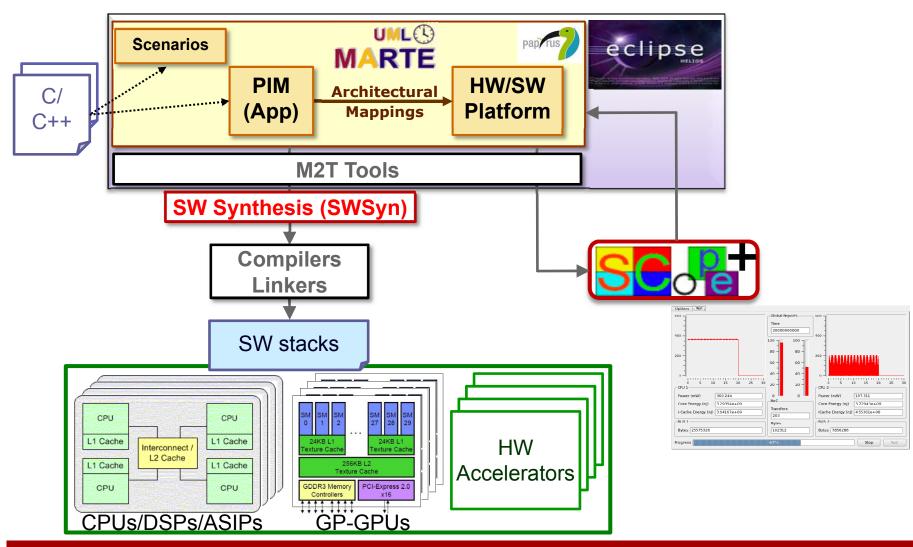

- Platform-Independent Model (PIM)

- Platform Description Model (PDM)

- Platform-Specific Model (PSM)

Rich semantics content

Simulation Analysis Single-source approach Verification Parallelization UML® Scenarios MARTE Performance PIM HW/SW Architectural Platform (App) Mappings Optimization Analysis **Design-Space** Architectural System Exploration Mapping Synthesis

## State-of-the-Art

### Discussion

- System modeling in MARTE

- Methods based on specific MoCs and/or profiles

- Requiring additional semantics

- Non-standard

#### SW Synthesis

- Commercial code generation available

- Limited support for heterogeneity

- Limited flexibility for different architectural mappings

- Limited support for the MARTE semantics

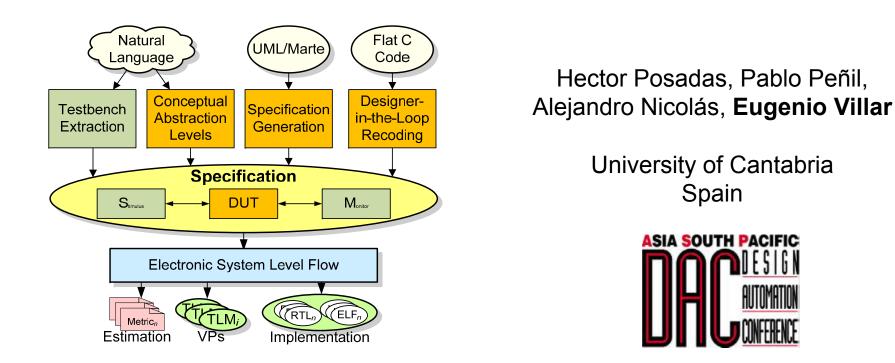

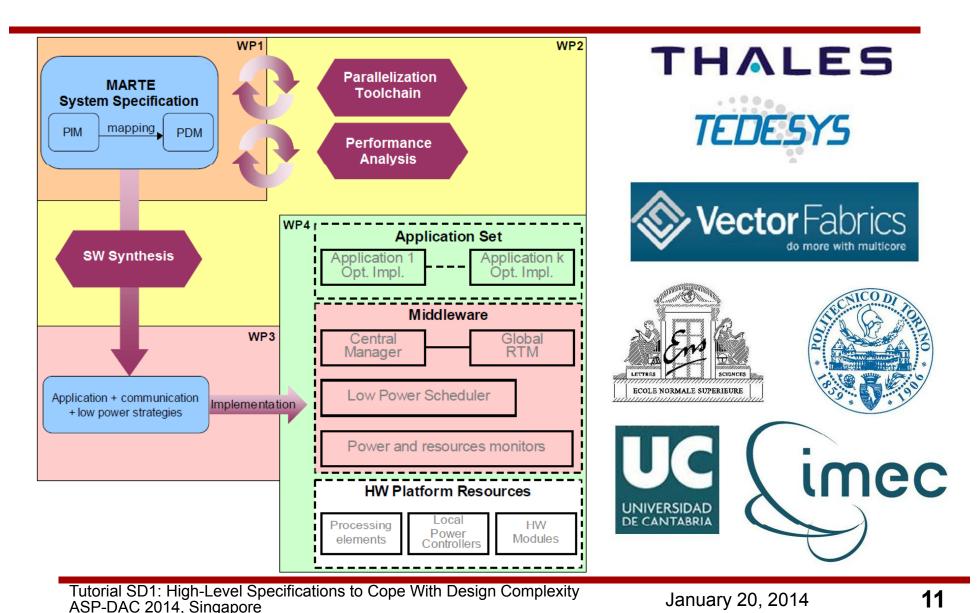

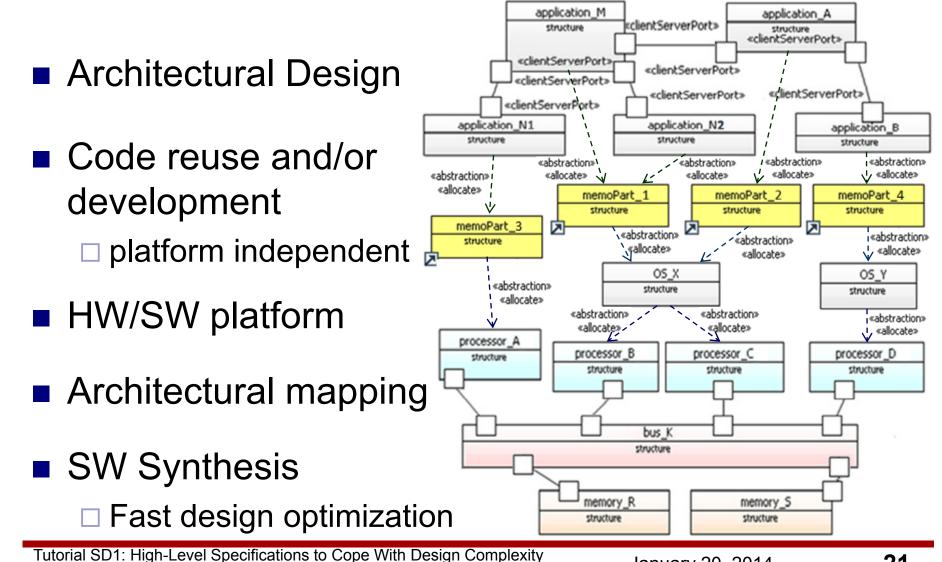

# **PHARAON Single-Source Design Flow**

# **PHARAON Single-Source Design Flow**

#### Main features

□ MDD concepts

- Separation of Concerns

- □ CBE: Component-Based Engineering approach

□ SW centric

Standard

MARTE profile

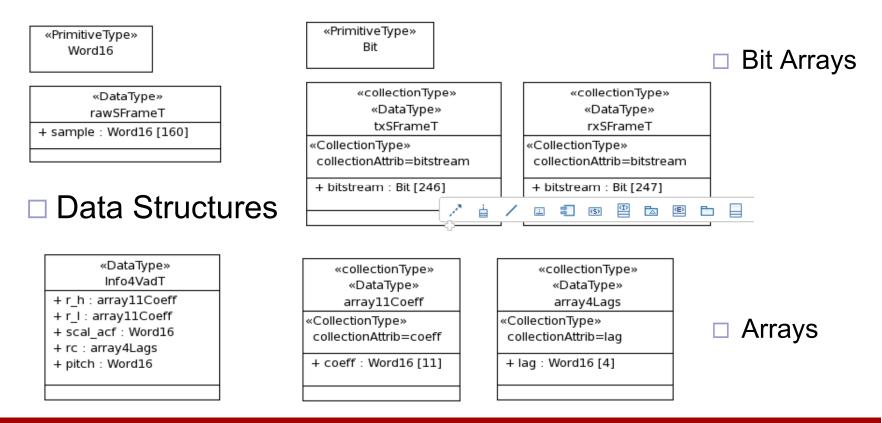

Data Types for Communication Interfaces

Primitive Types

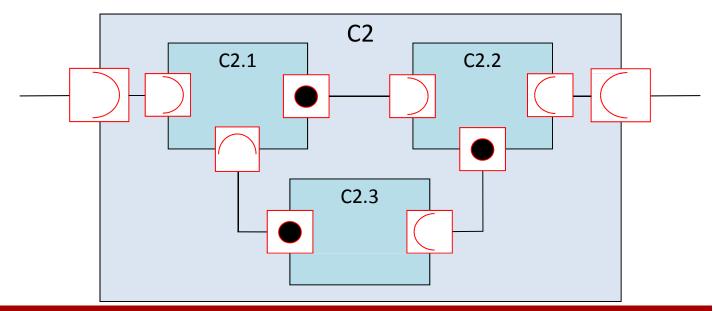

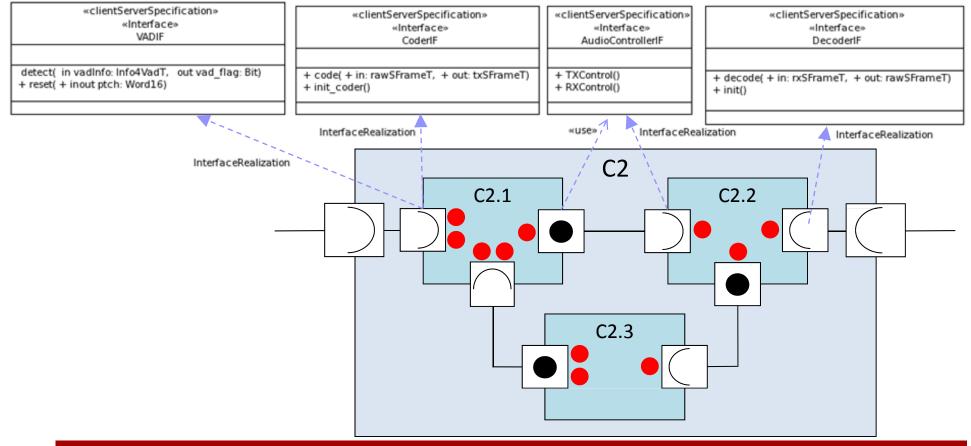

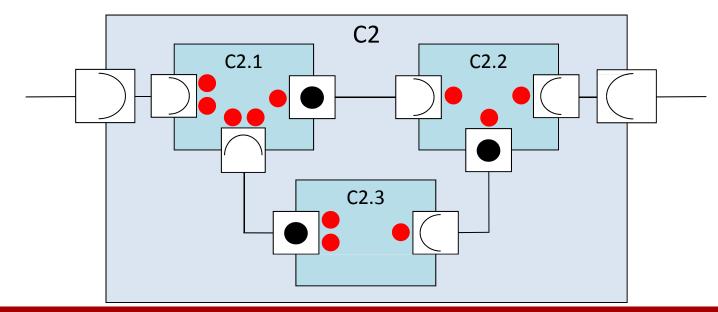

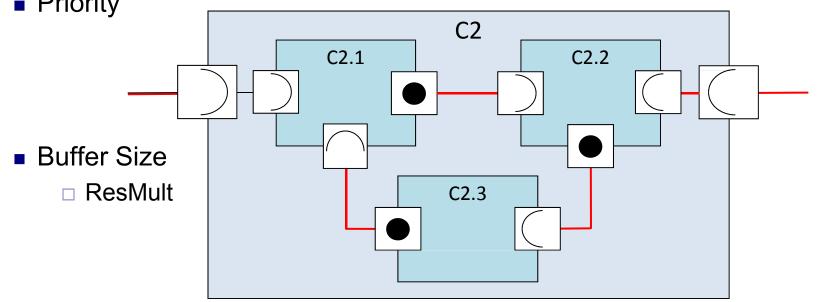

### Component model

□ Hierarchical functional encapsulation

- Ports

- provided or required

#### Component Interfaces

#### Component model

- Interfaces

- sequential, guarded or concurrent, Max. threads available

- argument sizes (data splitting), Num. of incoming channels

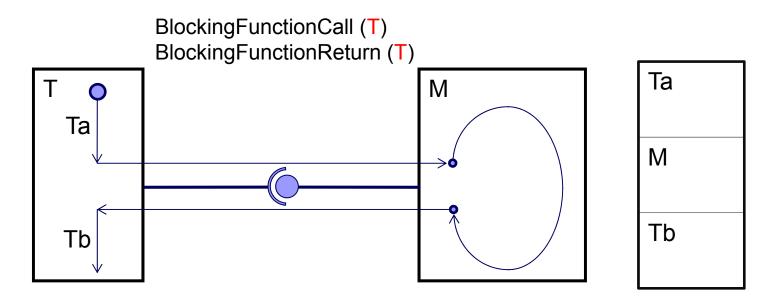

### Component model

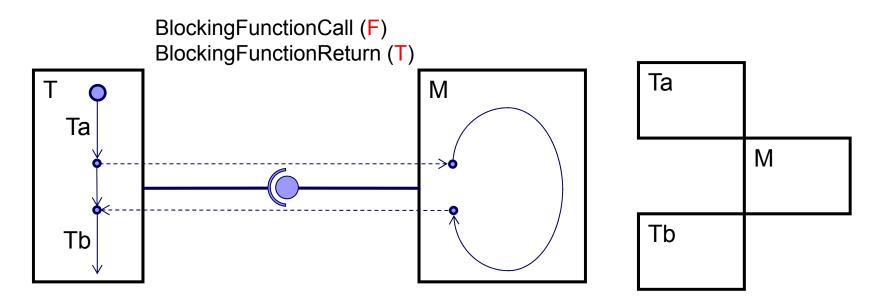

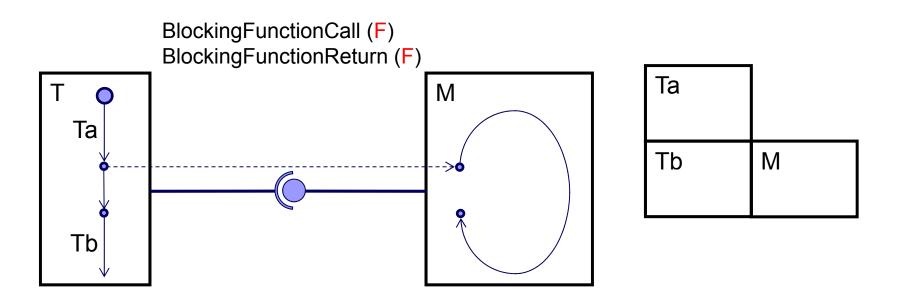

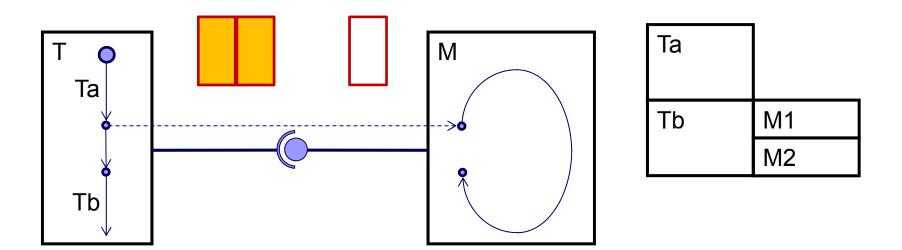

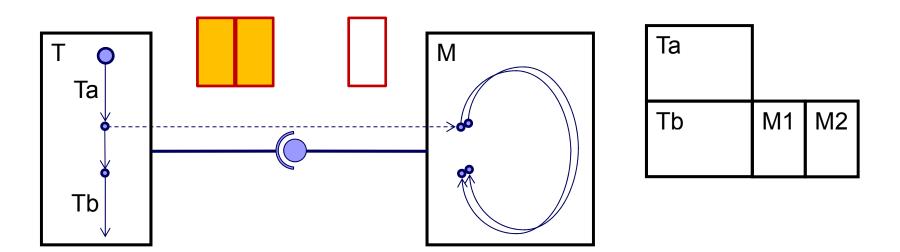

- Channels manage communications

- BlockingFunctionCall, BlockingFunctionReturn, both or none

- Timeout

- Priority

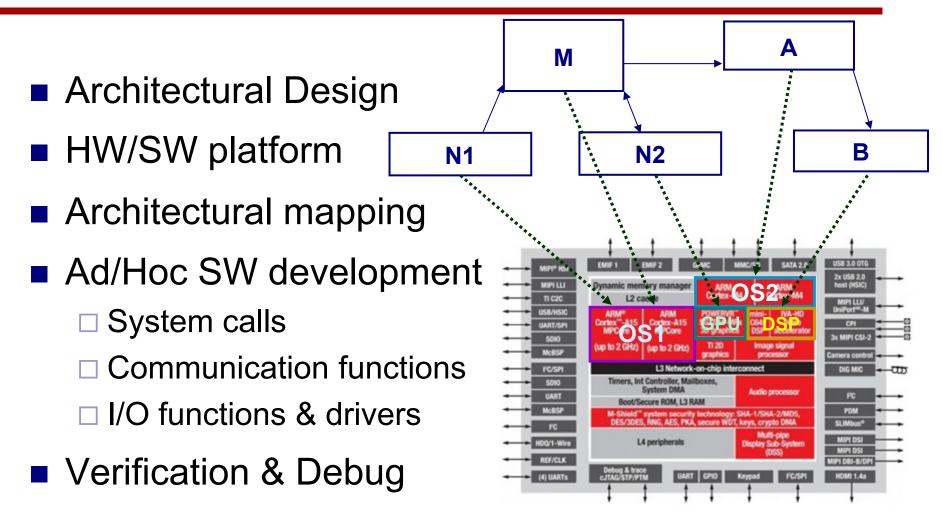

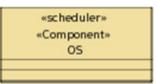

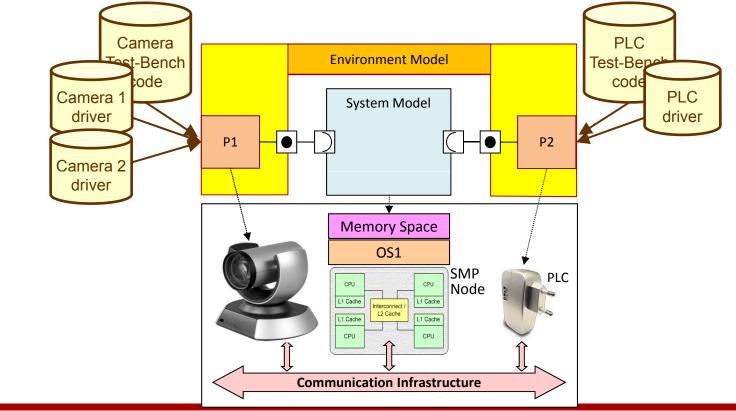

#### The Platform Description Model

- HW/SW Components using MARTE stereotypes

- Software Components

- □ OS, HdS, Drivers, …

- Hardware Components

□ Processors, Memories, Buses, Custom HW, I/O

ASP-DAC 2014, Singapore

January 20, 2014

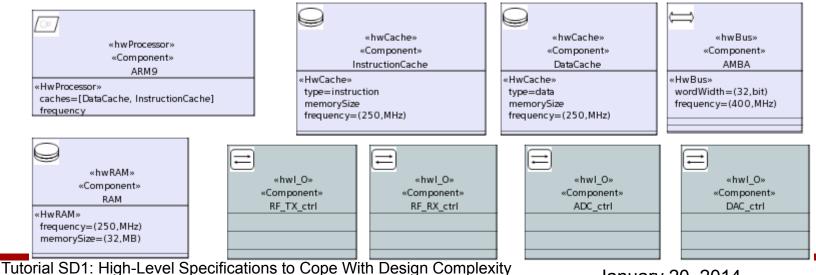

#### Platform-Specific Model

- Memory spaces mapped to platform resources

- □ Mapping of functional components

- to memory spaces and/or platform resources

ASP-DAC 2014, Singapore

January 20, 2014

- System heterogeneity

- Full support for

- □ any architectural mapping decided for each component

- □ any specific processing resource selected

- any processing resource type

- □ any memory space

- □ any OS used by the processing resource

- □ any communication infrastructure

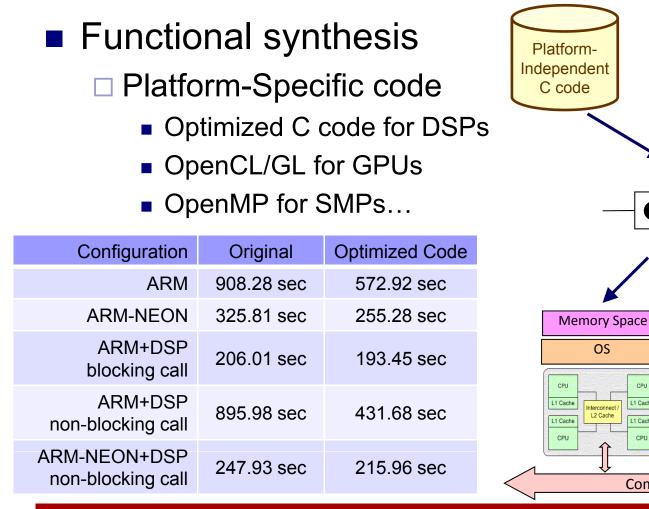

Functional synthesis

- One executable per memory-space

- □ Platform-Independent (C/C++) code

- Highest reusability

- Non-recommended explicit calls to platform services

- $\Box$  communication, concurrency, etc.

- Platform services should derived from the UML/MARTE model

- POSIX and/or OpenMP as alternatives

- Static execution flows

- <<SwSchedulableResource>>

GPU

PCI-Express 2.0

SDDR3 Memor

DSP

optimized

C code

## SW Synthesis

**Communication Infrastructure**

SMP

node

CPU

L1 Cache

L1 Cache

CPU

**OpenCL/GL**

code for

GPU

**C**3

24

DSP

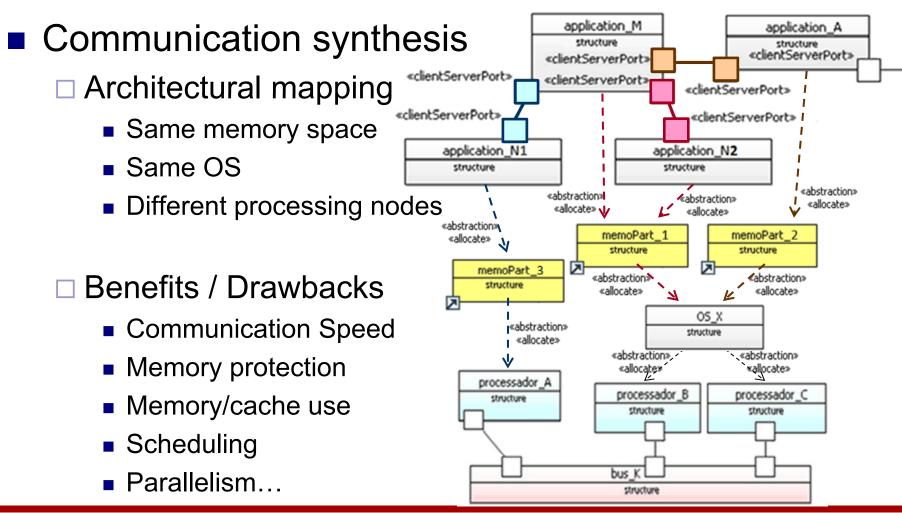

- Essential activity in heterogeneous SW synthesis

- □ Client-Server paradigm

- Dependent on the architectural mapping

- □ 3 Layers automatically inserted in service calls

- Layer 1: communication semantics

Allocation independent

- Layer 2: management for allocation-dependent communications

Thread generation, data splitting, synchronization

- Layer 3: Low-level communications

- □ Inter-thread, Inter-process, distributed communication

### Communication synthesis

- □ Layer1: Independent of architectural mapping

- Channel properties

□ RPC

- □ Layer1: Independent of architectural mapping

- Channel properties

- Pipeline

- □ Layer1: Independent of architectural mapping

- Channel properties

- Description Pipeline & Parallel

- □ Layer1: Independent of architectural mapping

- Interface properties

- Data splitting

- □ Layer1: Independent of architectural mapping

- Interface properties

- Data splitting

### Implementation alternatives

- □ Channel semantics can be implemented in multiple ways

- Different OS services

- □ shared memory

- message queue

- □ socket

- □ file...

- Performance is highly dependent on platform and OS

- □ Synthesis enables fast exploration

- optimal channel implementation for specific platform and code

### MultiCore Association APIs

- Standard APIs for communication and synchronization

- Closely distributed embedded systems

- MCAPI communication

- MRAPI synchronization

- MTAPI task generation

- Independence from OS

- □ OS-agnostic channel implementation

- Components treated as MCAPI nodes

- Ports treated as MCAPI endpoints

#### Platform Inputs & Outputs

□ Drivers associated to environmental components

## Conclusions

### UML/MARTE

- □ Powerful modeling methodology

- □ Single-Source approach

- Platform-Independent Modeling

- □ Maximizing reusability

# Conclusions

### SW Synthesis

- Functional modeling

- Functional synthesis

- Communication synthesis

- Platform Inputs & Outputs

Actually enables platform-independent code

- Reduces in-depth knowledge of platforms

- Support shorter design optimization cycles

- wider design exploration

- shorter code generation on heterogeneous platforms

# **Additional Information**

- http://www.teisa.unican.es/gim/en/proyecto?id=95

- H. Posadas, P. Peñil, A. Nicolás, E. Villar "Automatic synthesis of embedded SW for evaluating physical implementation alternatives from UML/MARTE models supporting memory space separation" Microelectronics Journal, in press, doi: 10.1016/j.mejo.2013.11.003.

- H. Posadas, E. Villar, et al.

"EU FP7-288307 PHARAON project: Parallel and heterogeneous architecture for real-time applications"

Euromicro Conference on Digital System Design, DSD 2013, IEEE, doi:

- 10.1109/DSD.2013.47.

- H. Posadas, P. Peñil, A. Nicolás, E. Villar

"System synthesis from UML/MARTE models: The PHARAON approach", Electronic System Level Synthesis Conference, ESLsyn, 2013, IEEE.

- P. Peñil, H. Posadas, A. Nicolás, E. Villar "Automatic synthesis from UML/MARTE models using channel semantics" International Workshop on Model-Based Arquitecting and Construction of Embedded Systems, ACES-MB 2012, doi: 10.1145/2432631.2432640.