# Software Simulation Technologies in Virtual Platforms

Class 6: "Embedded Software Development on Virtual Platforms – Are you ready for Industrial Deployment?", Embedded World 2013, Nuremberg 26/2/2013

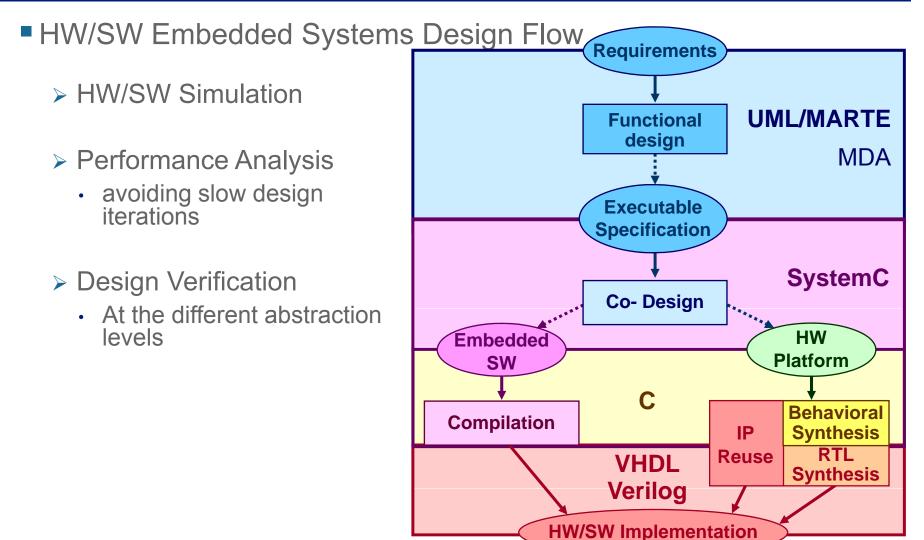

## Context

Class 6: "Embedded Software Development on Virtual Platforms – Are you ready for Industrial Deployment?", Embedded World 2013, Nuremberg 26/2/2013

## Agenda

- Motivation

- > Why SW performance analysis

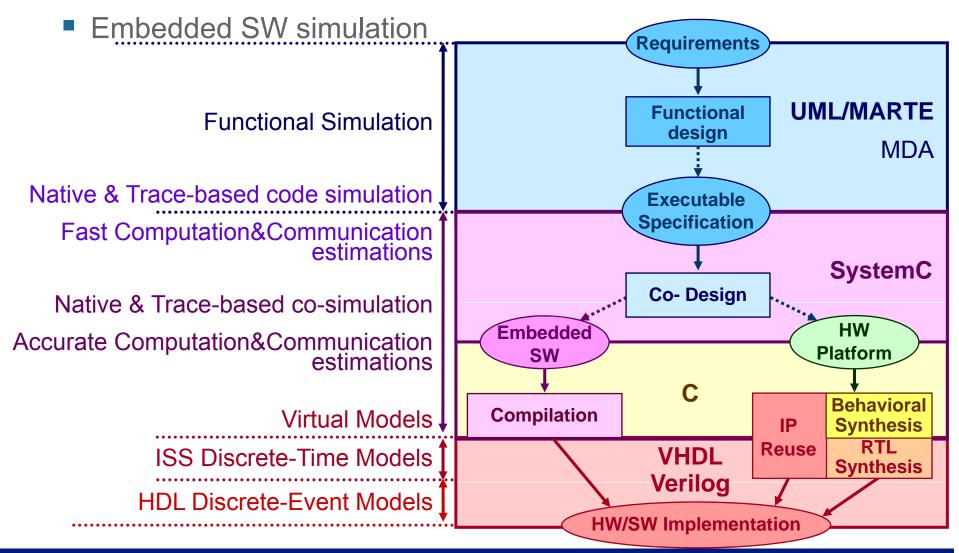

- Software Simulation Technologies in Virtual Platforms

- Simulation Technologies at different abstraction levels

- SCoPE: SW performance analysis for DSE

- Native simulation

- After architectural mapping

- SCoPE<sup>+</sup>: SW performance analysis for DSE

- Compositional Native simulation

- Before architectural mapping

- Direct PSM from the same PIM

- Conclusions

#### Motivation

- The MPSoC

- Multi-processing platform

- ASIC

- FPGA

- Commercial multi-processing platform

- SW-centric design methodology

- Most of the functionality implemented as Embedded SW

- With 'some' application-specific HW

Class 6: "Embedded Software Development on Virtual Platforms – Are you ready for Industrial Deployment?", Embedded World 2013, Nuremberg 26/2/2013

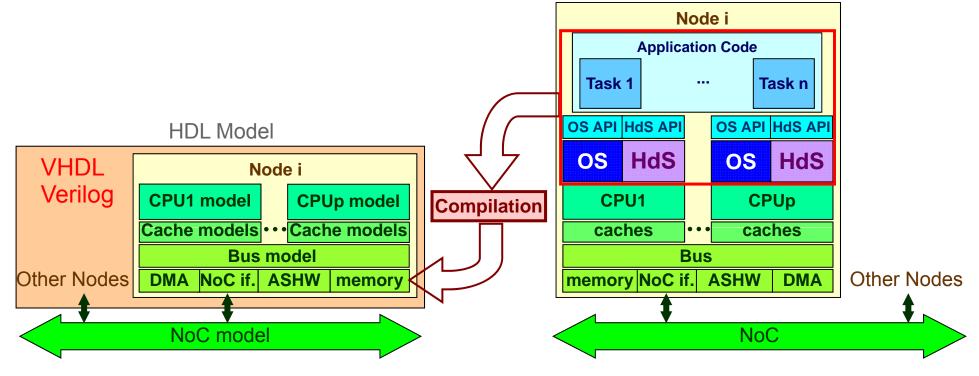

- HDL simulation

- Very detailed Model

- Very accurate

- Very slow

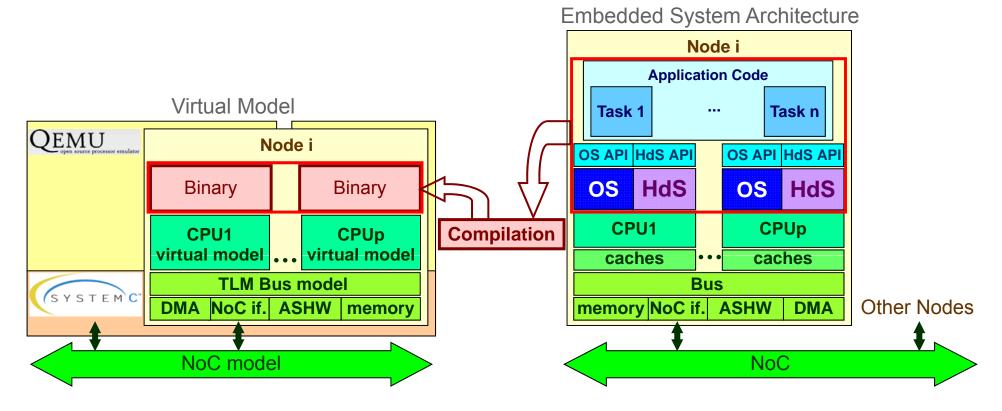

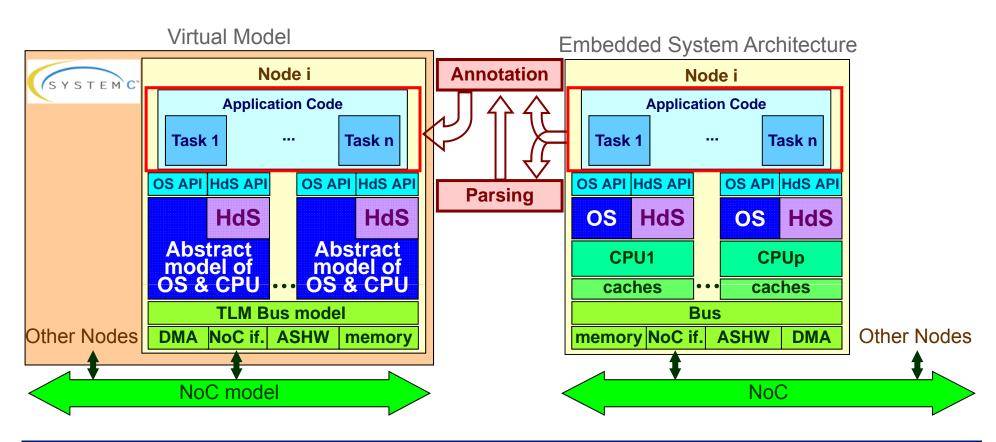

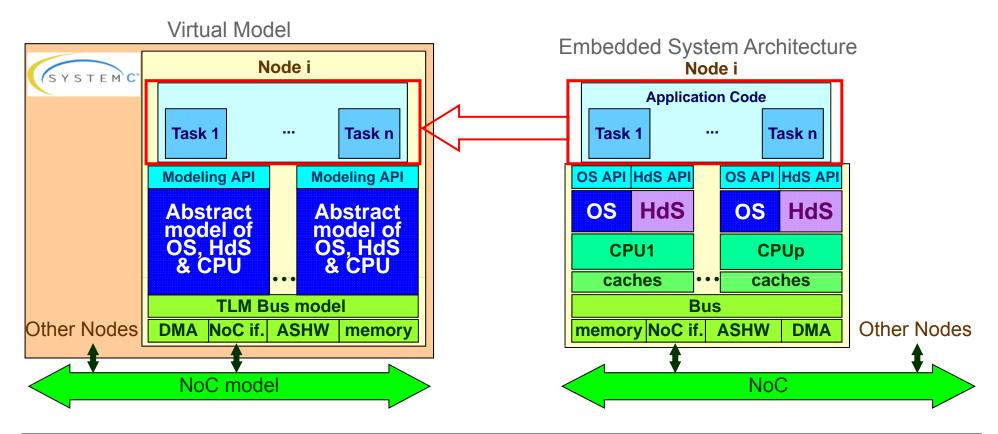

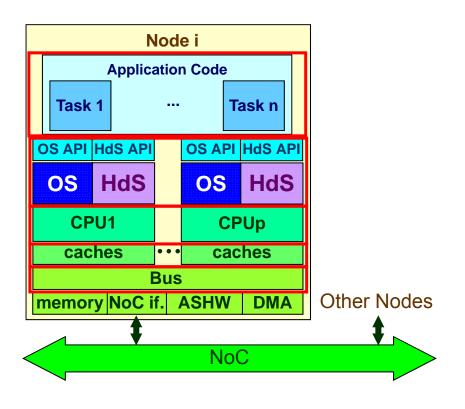

Embedded System Architecture

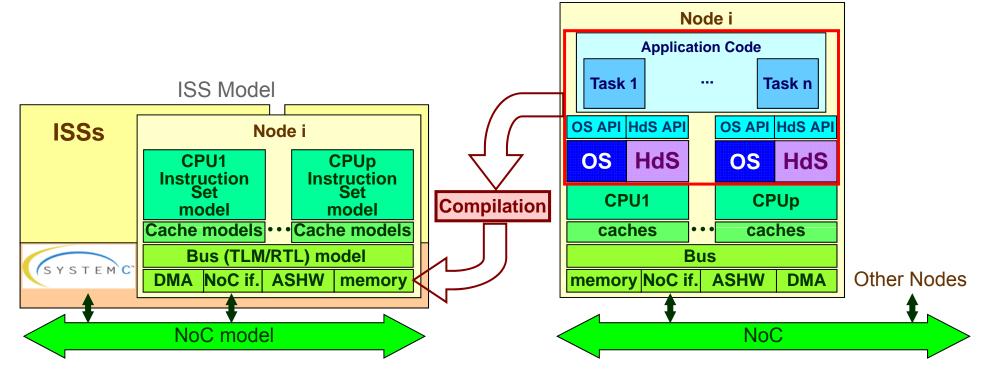

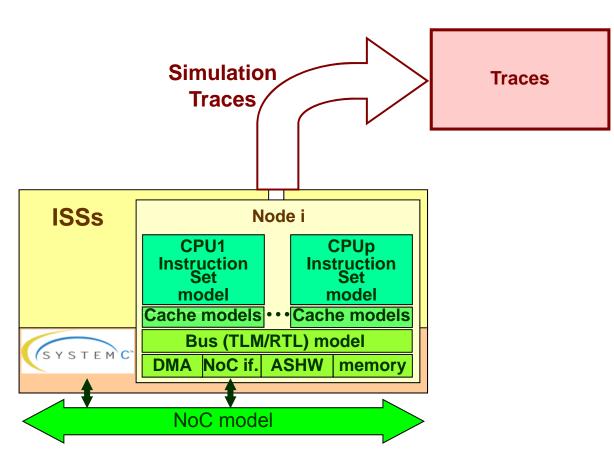

- ISS simulation

- Very detailed Model

- Very accurate

- Very slow

Embedded System Architecture

- SW Simulation Technologies

- Virtualization

- Target virtual model on host

- Virtualization (QEMU)

- Detailed model

- High modeling cost

- Late design steps

- Faster than ISS

- SW Simulation Technologies

- Virtualization

- Functional emulation

- Rough timed simulation

- i.e. 1 cycle per instruction

- > Additional effort needed for more accurate modeling

- Execution times

- Power consumption

- Caches

- ...

- Requires a specific Virtual Model for each processor

- Commercial tools

- > OVP, FastModels, Cadence, Carbon, Synopsys (CoWare), etc.

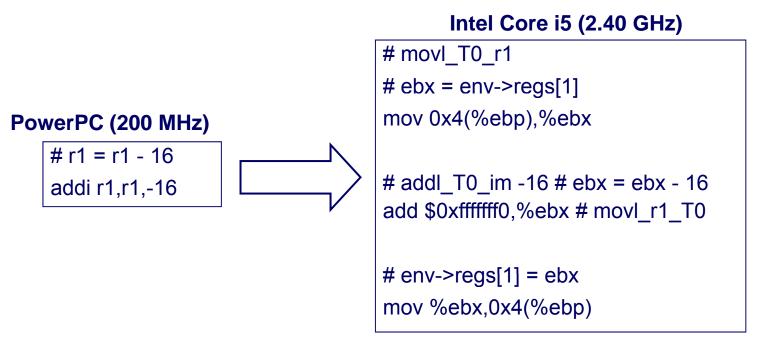

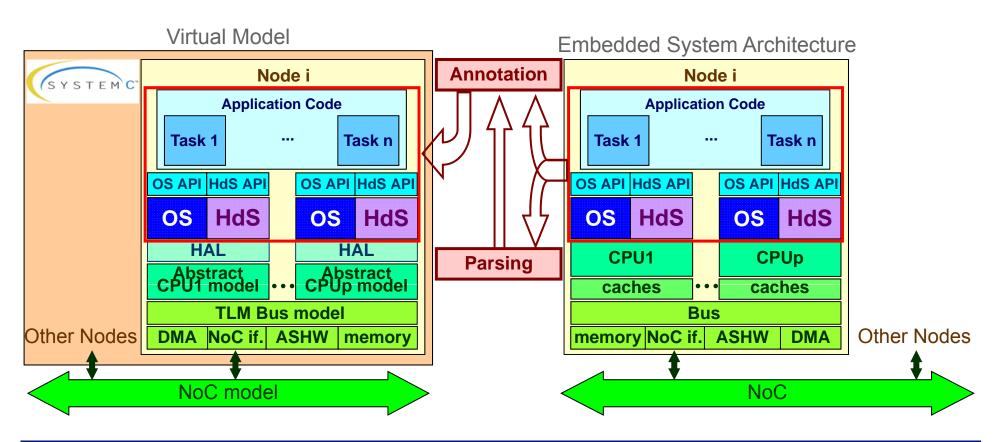

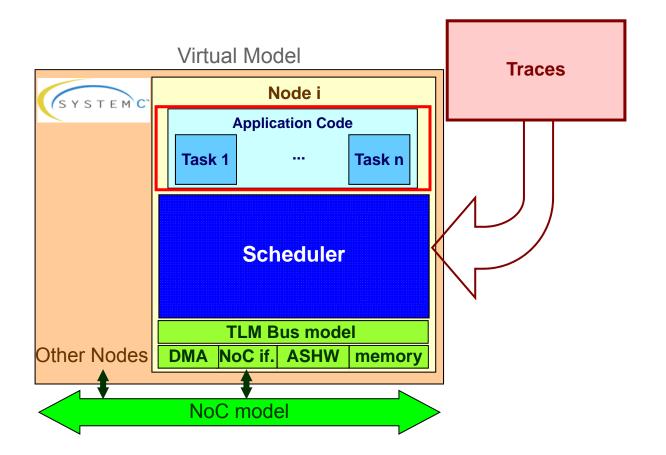

- SW Simulation Technologies

- Native & Trace-based simulation

- Embedded code directly executed by the host

- Good accuracy

- Native back-annotation

- Trace analysis

- Fast execution time

- SW Simulation Technologies

- Native simulation based on HAL API

- Abstraction of the HW platform

- SW Simulation Technologies

- Native simulation based on OS API

- Abstraction of the SW platform

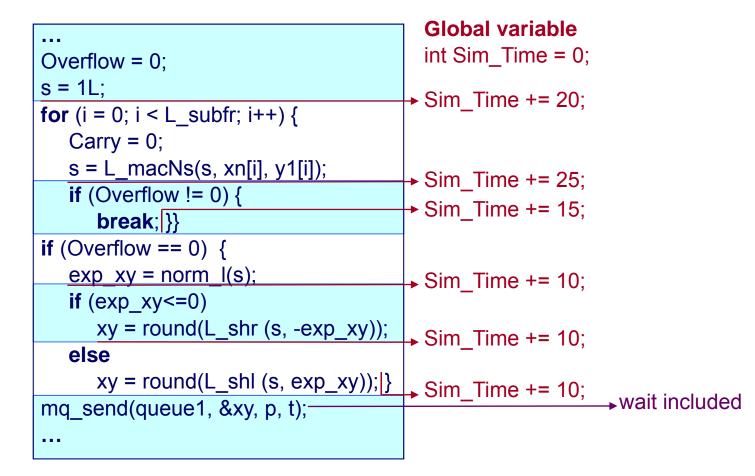

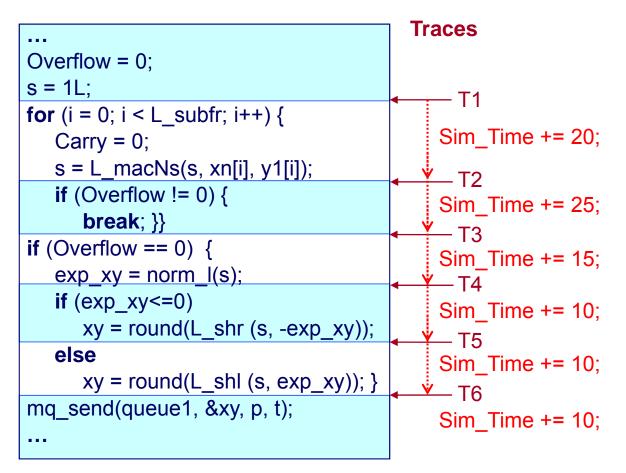

- SW Simulation Technologies

- Basic code annotation in native simulation

- Trace-based simulation

- Activity traces from detailed models

#### Embedded System Architecture

Class 6: "Embedded Software Development on Virtual Platforms – Are you ready for Industrial Deployment?", Embedded World 2013, Nuremberg 26/2/2013

- SW Simulation Technologies

- Trace-based simulation

- SW Simulation Technologies

- Trace-based simulation

- Difficult scheduling in complex multi-processing systems

- SW Simulation Technologies

- Basic code execution in trace-based simulation

- Functional simulation based on code

- Fastest but least accurate

- Work-load analysis

#### Performance/Error comparison

|                       | Technology  | Time<br>Estimation | Time & Power<br>Estimation |

|-----------------------|-------------|--------------------|----------------------------|

| Functional            | Performance | 5,000              | N.A.                       |

|                       | Error       | N.A.               | N.A.                       |

| Native<br>Trace-based | Performance | 1,000              | 500                        |

|                       | Error       | 1.3                | 1.4                        |

| Virtualization        | Performance | 200                | T.B.M.                     |

|                       | Error       | 1.5                | T.B.M.                     |

| ISS                   | Performance | 10                 | 1                          |

| (cycle-accurate)      | Error       | 1.1 (DT)           | 1.1                        |

| HDL                   | Performance | 1                  | 0.1                        |

|                       | Error       | 1 (DE)             | 1                          |

Rough approximate figures

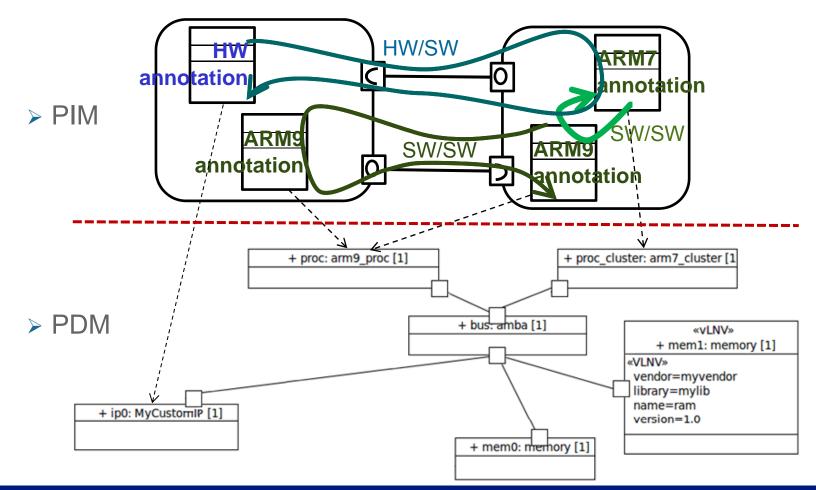

- Key features

- Abstract OS modeling

- Instruction cache modeling

- Data cache modeling

- System power estimation

- Novel features

- > Physical memory accesses

- Separate memory spaces

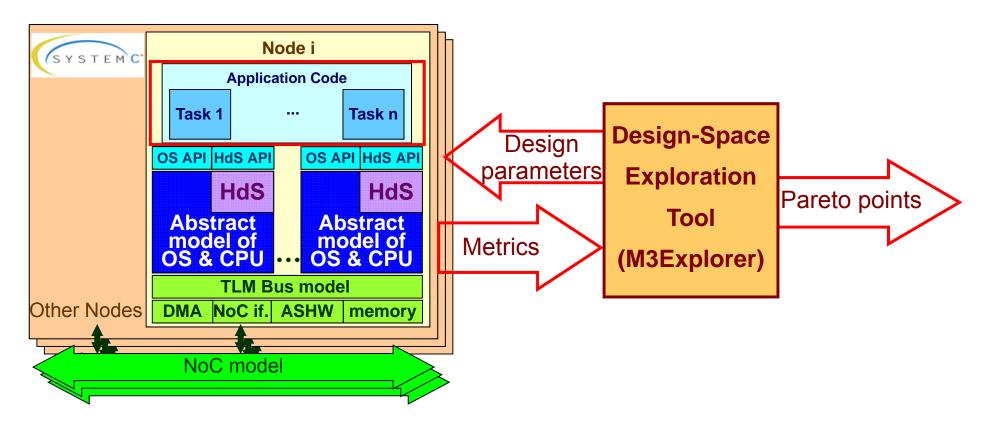

- Configurability for Design-Space Exploration

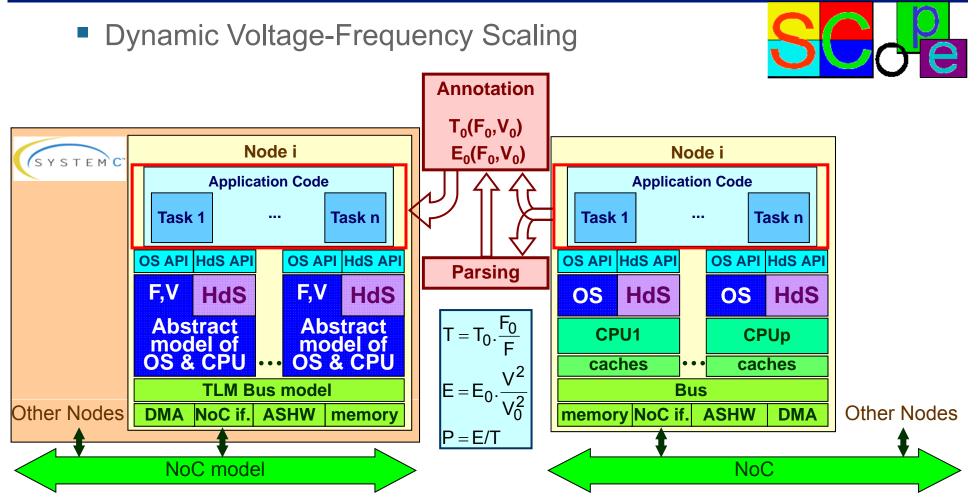

- Dynamic Voltage-Frequency Scaling

- > Thermal modeling

- System composition from IP-XACT components

- Win32 API

- System power estimation

- > Application code

- Instruction counting from binary

- > OS & HW-dependent SW

- Function power estimation

- Caches

- Counting memory accesses

- Cache misses

- ≻ Bus

- Actual bandwidth

- Cache misses

- DMA accesses

- HW accesses

- > HW & NoC

- SystemC power models

Design-Space Exploration

Configurable model

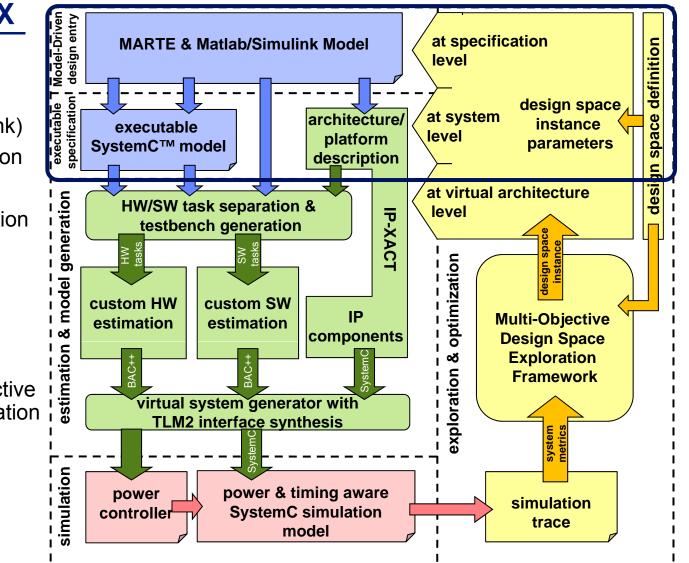

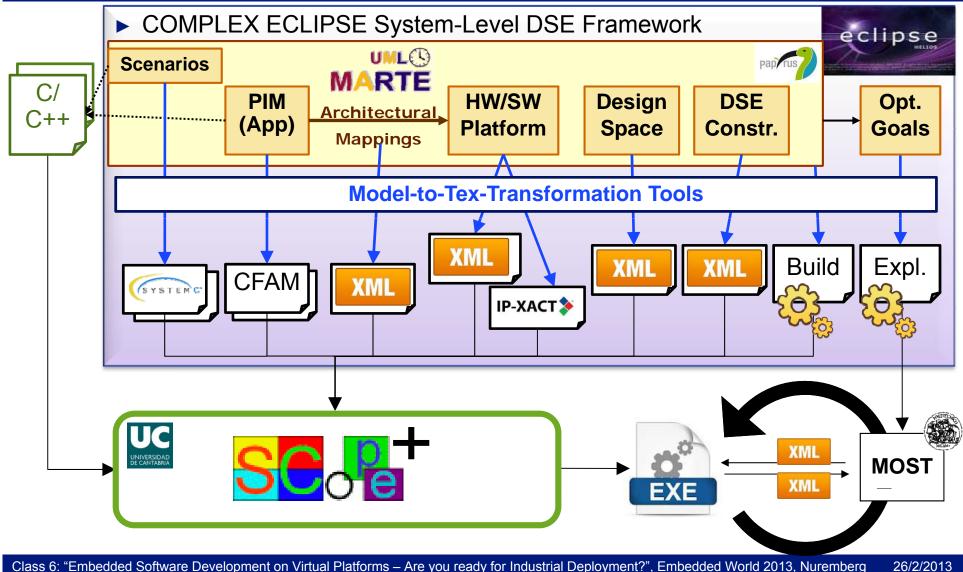

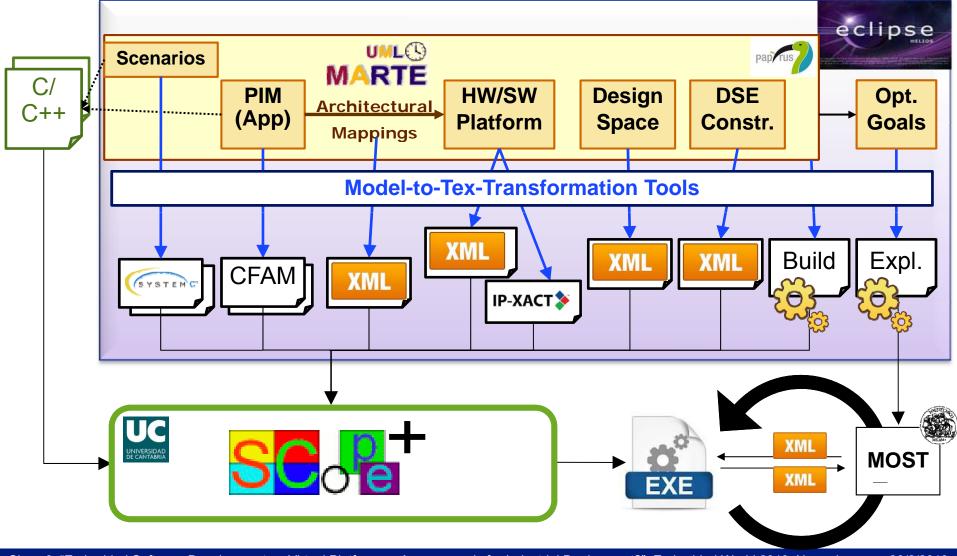

#### The COMPLEX Framework

- Model-Driven Design entry (MARTE/Simulink)

- Executable specification

- Power/Timing Estimation & Model Generation

- Power/Timing aware SystemC simulation

- Automatic Multi-Objective Design-Space Exploration

- ▶ at system-level

- ▶ at block-level

SEVENTH FRAMEWORK

PROGRAMME

# SCoPE+: Compositional Native Performance Estimation

- Implementation-Agnostic Platform Independent Frontend

> CFAM-CM API

- Fulfilling COMPLEX UML/MARTE executive semantics

- System-Level Modeling of Multi-OS execution

- SW/SW-HW/SW-HW/HW communications

- > Architectural mapping agnostic

- Taking advantage of the native simulation speed\*accuracy

## CFAM-CM

- Macros and functions

- Concurrent Functional Application & Component Model

- Component Based PIM

- CFAM API

- Platform services required by functional code

- > Hide RTOS specific calls

#### **CFAM-CM**

Platform-Dependent Estimations directly on the PIM

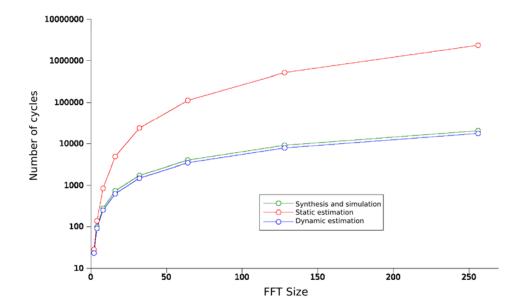

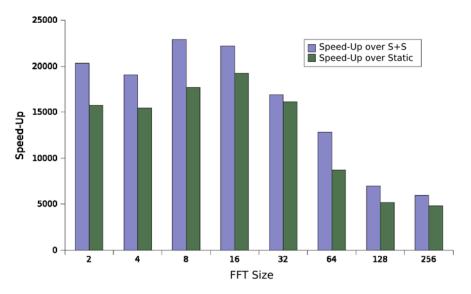

#### High-Level Custom HW Estimation Methodology

#### ► 30 High-Level Custom HW Estimation Methodology

- Accuracy vs

- > HL-Synthesis and Simulation

- > Static

- > (RTL model as golden model)

- Speed-Up vs

HL-Synthesis and Simulation

Static

University of Cantabria

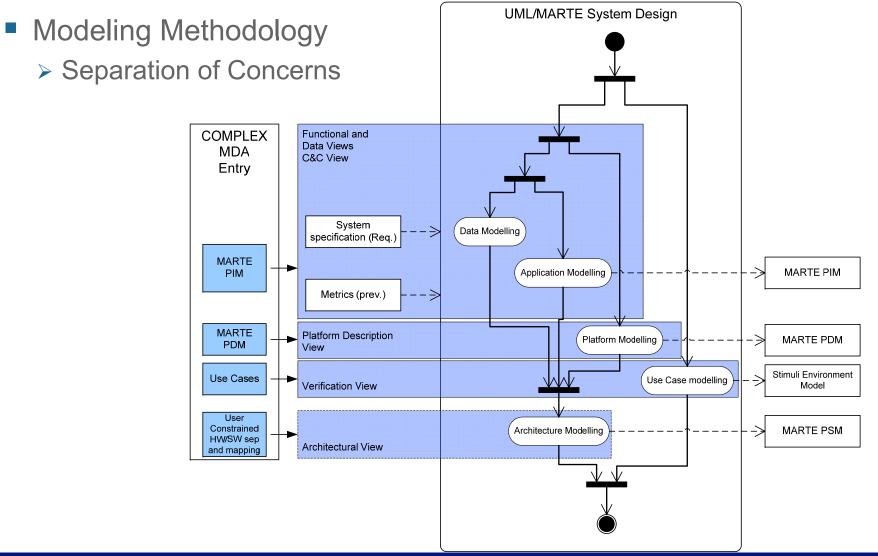

#### The COMPLEX Eclipse System-Level DSE Framework

Class 6: "Embedded Software Development on Virtual Platforms – Are you ready for Industrial Deployment?", Embedded World 2013, Nuremberg 26/2/2013

- Main features

- MDD concepts

- Separation of Concerns

- CBE: Component-Based Engineering approach

- SW centric

- DSE oriented

- > UML-based

- MARTE profile

- Capture most of the RTE required semantics

- COMPLEX profile

- Defines DSE specific aspects not covered by MARTE

#### UNIVERSIDAD DE CANTABRIA Cantabria

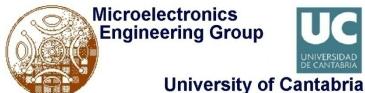

- PIM Modeling: Data View

- Data Types for Communication Interfaces

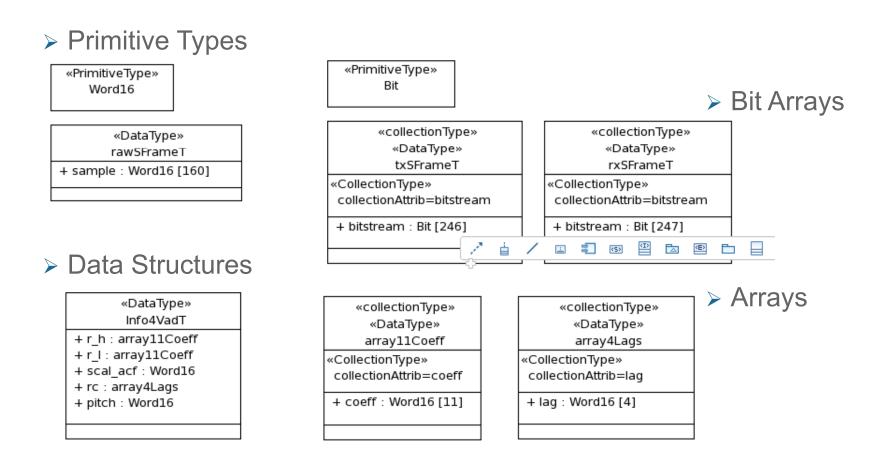

- **PIM Modeling: Functional View**

- Data Types for Component Interfaces and Functional Classes

Classes implement Interfaces and require services of other interfaces

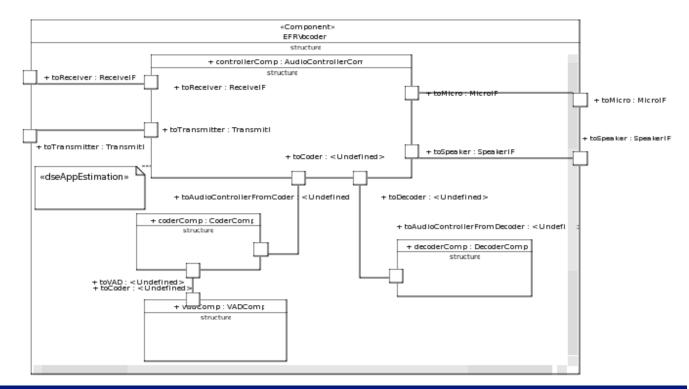

# **PIM Modeling: Communication & Concurrency View**

- Application Component Architecture

- > As a Composite Diagram

- Application components

- Provided and required operations

Class 6: "Embedded Software Development on Virtual Platforms – Are you ready for Industrial Deployment?", Embedded World 2013, Nuremberg 26/2/2013

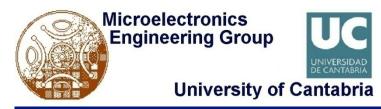

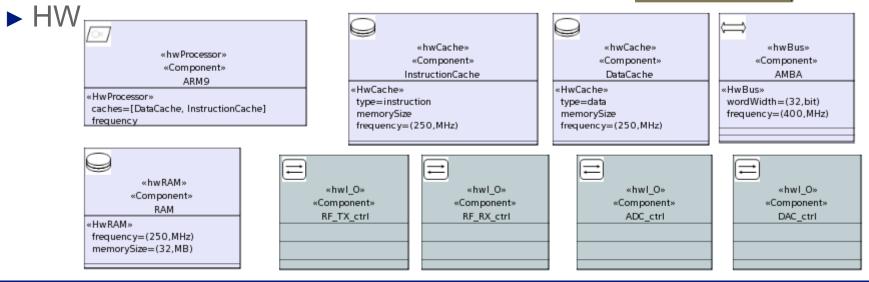

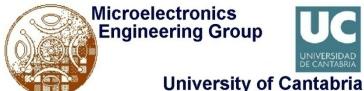

# Platform View: The Platform Description Model

- HW/SW Components of the Platform

- Software Components

- OS, Drivers, ...

- Hardware Components

- Processors, Memories, Buses, Custom HW, I/O

- Components using MARTE stereotypes

- Architectural View: The Platform-Specific Model

- Composite Diagram

- > Application Component Instances

- > Architectural Mapping

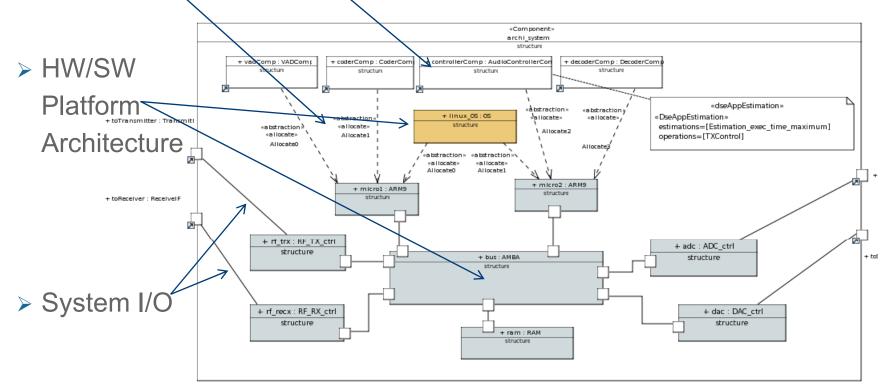

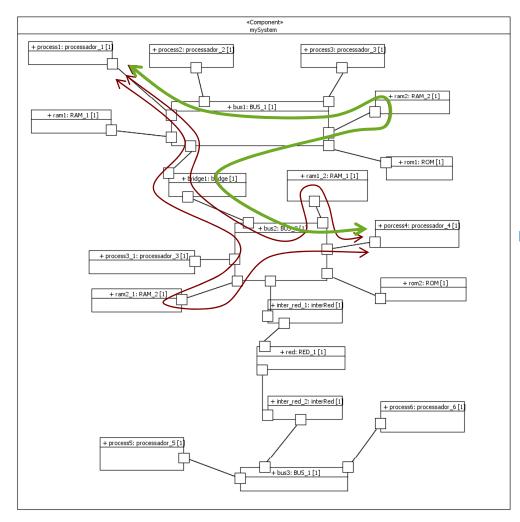

#### Architectural View: Data Path Alternatives

- Several routing alternatives possible

- Which data path to communicate processors 1 and 4?

- Impact on Performance

- Solution 1: The estimation tool (SCoPE+) selects one path:

> Optimum: #hops, hop cost

#### Architectural View: Data Path Alternatives

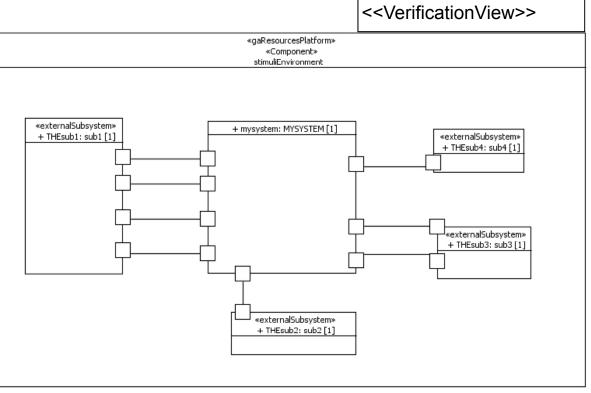

verification

- Verification View: Environment Components

- Automatic generation of the SystemC Test-Bench

- COMPLEX <<VerificationView>> stereotype

- Homogeneous style

- Composite diagram

Class 6: "Embedded Software Development on Virtual Platforms – Are you ready for Industrial Deployment?", Embedded World 2013, Nuremberg 26/2/2013

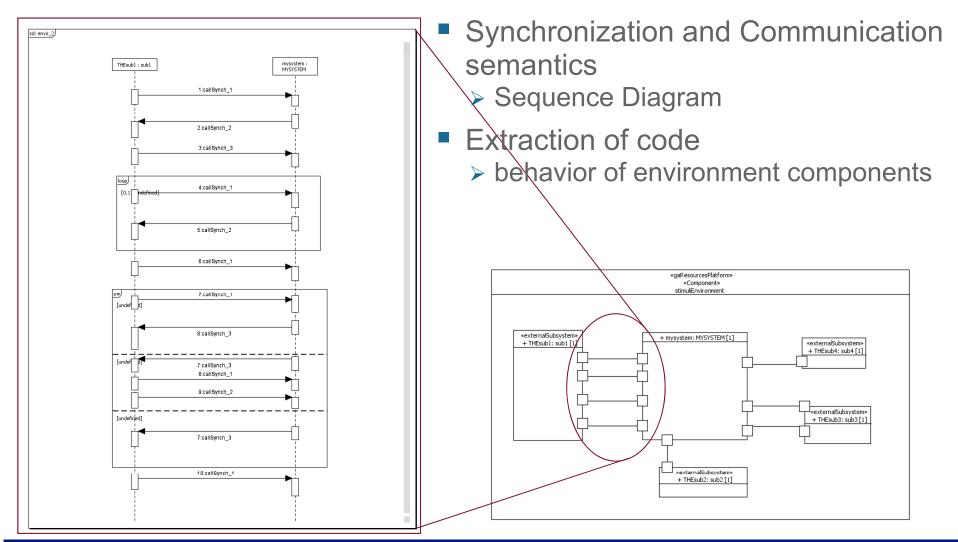

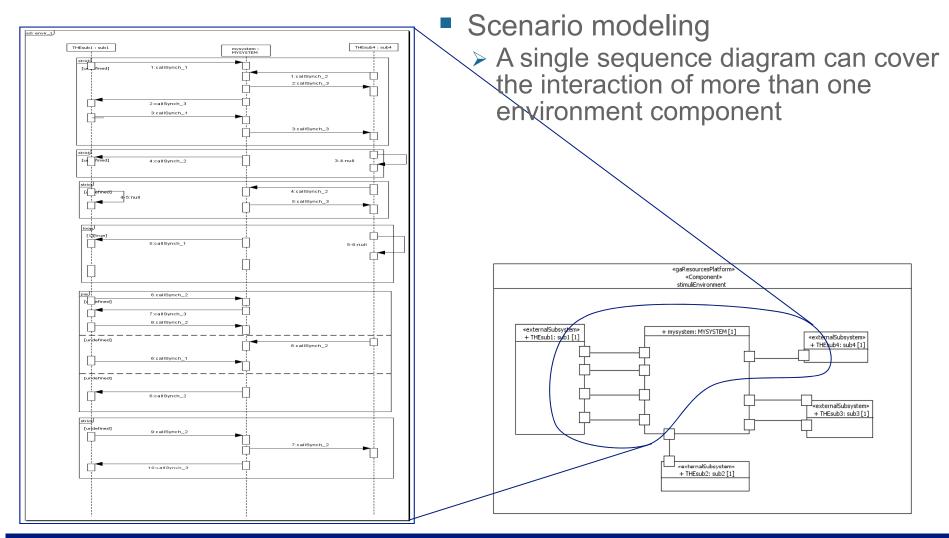

### Verification View: Interaction between system and environment

#### Verification View: Interaction between system and environment

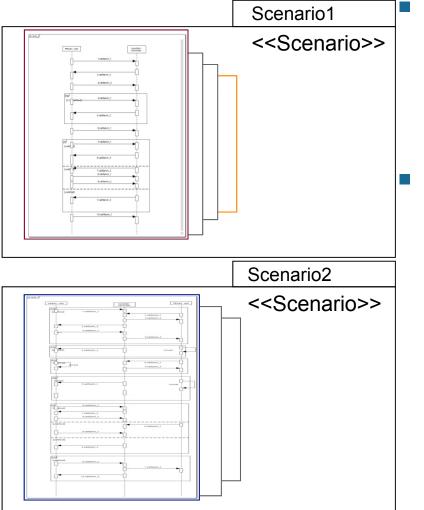

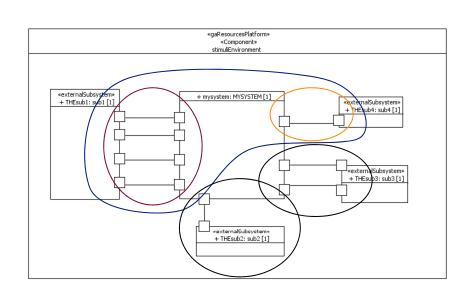

#### Verification View: Scenarios

Scenario: A tuple of interactions covering the interaction of the system with the whole environment > A package within the Verification View > with the <<Scenario>> stereotype Several scenarios are possible

Class 6: "Embedded Software Development on Virtual Platforms – Are you ready for Industrial Deployment?", Embedded World 2013, Nuremberg 26/2/2013

# Modeling the Design Space: General Features

- Capturing the Exploration Space in a single model

- Defining a set of Scenarios

allowing the selection of the scenarios to be explored

- Defining the Output metrics

- > used as input to the selection of the next experiment

- determining the Pareto points

- The Design Space is composed of

- A set of Architectural Mappings

- A set of configurable attributes for Platform Components

- A set of Platforms

- A set of DSE Constrains and rules

### Conclusions

- SW simulation and performance analysis

- Essential Design Technology

- > HW/SW Embedded Systems

- At different design steps

- Different modeling and simulation technologies

- Various performance\*accuracy products

- UML/MARTE Modeling Methodology

- MDD concepts

- Separation of Concerns

- CBE: Component-Based Engineering approach

- SW centric

- DSE oriented

- > Automatic Model Generation

Thamk You!

- Additional Information

- COMPLEX Website

- <u>http://complex.offis.de</u>

- COMPLEX plug-in

- <u>https://complex.offis.de/eclipseupd</u>

- Microelectronics Engineering Group

- http://www.teisa.unican.es/gim/en/tema?id=4

- SCoPE

- <u>http://www.teisa.unican.es/scope</u>

- Eugenio Villar

- villar@teisa.unican.es